Tutorial 2: Heterogenous Integration (HI) using advanced packaging

Автор: VLSID 2022

Загружено: 2022-03-22

Просмотров: 427

Описание:

Tutorial 2: Heterogenous Integration (HI) using advanced packaging

Speakers: Arun Chandrasekhar & Rupesh Pothineni (Intel)

Tutorial Abstract:

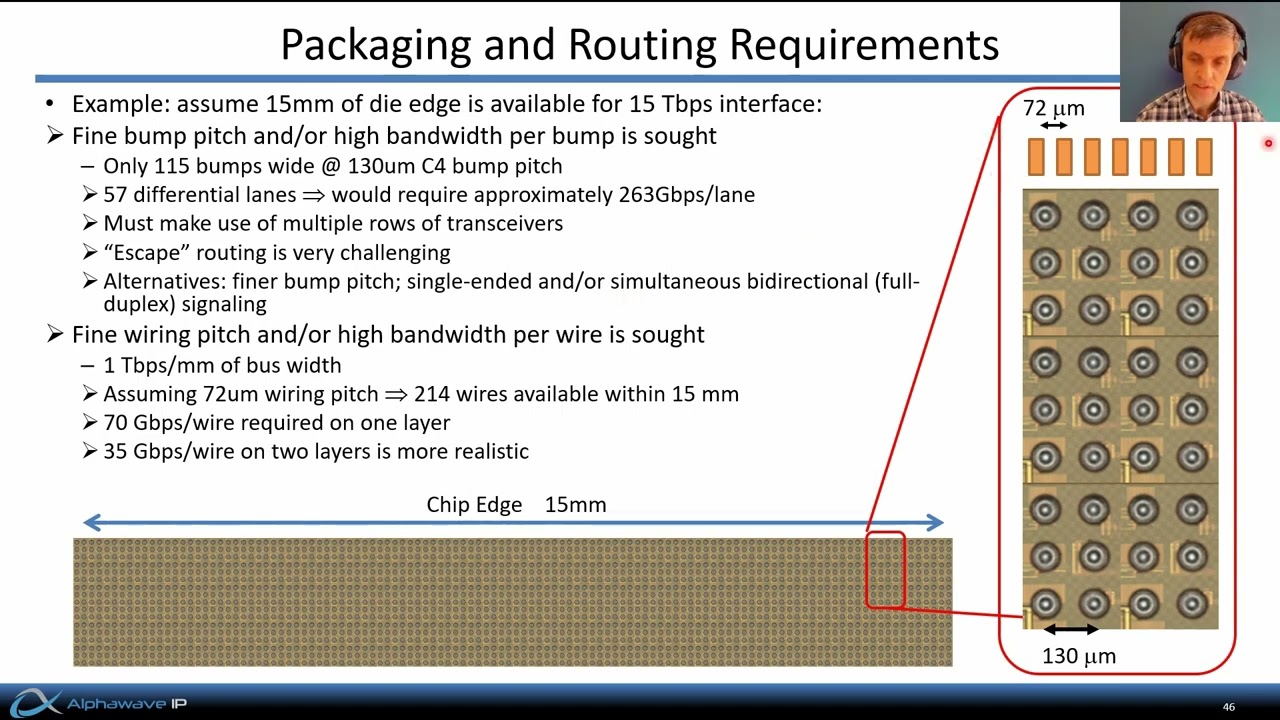

In this tutorial the presenters will cover the basics of Heterogeneous Integration (HI) starting with how Moore’s law has evolved and the different schemes of disaggregation (such as 2D, 2.5D & 3D). The tutorial will then move into the methods and techniques of design partition under disaggregation. This will be followed by the an overview of the advanced package technology offerings available at Intel & from OSATs along with a couple of case studies highlighting the complexities involved. Finally an overview of the various challenges facing us in advancing heterogeneous disaggregation in advanced packaging will be briefly discussed along with concluding remarks.

About Speakers:

Arun Chandrasekhar is a Senior Packaging Engineer in the Data Centre Group at intel. He has been with Intel, Bangalore for ~18 years and has primarily been the architect & designer for multiple generation of Xeon server and Xe graphics packages. He is also an adjunct faculty in the Dept. of Electrical Systems Engg. at IISc, Bangalore. He holds a PhD from IMEC, Belgium, M.Tech from IISc, Bangalore & B.E from the College of Engg. Guindy, Chennai

Rupesh is a principal engineer in IoTG silicon development Group at intel. He has been with Intel for 18+ years and played leadership roles in the convergence of several SoC. His expertise is in floorplan tech readiness, HIP methodologies, layout Integration/verification, die disaggregation (Foveros, EMIB, Co-EMIB, OSAT) methodology development for Client, Server, IoTG products. He holds MS from Bits.

Повторяем попытку...

Доступные форматы для скачивания:

Скачать видео

-

Информация по загрузке:

![[Eng Sub] TSV (Through Silicon Via) - HBM, кремниевый интерпозер, датчик изображения КМОП, MEMS](https://imager.clipsaver.ru/s5IBdqM07P8/max.jpg)