CMOS Inverter Layout Design with DRC and LVS using Pegasus in Cadence Virtuoso IC 23 (gpdk045)

Автор: TronicWorks Tech

Загружено: 2025-10-14

Просмотров: 805

Описание:

Welcome to TronicWorks Tech!

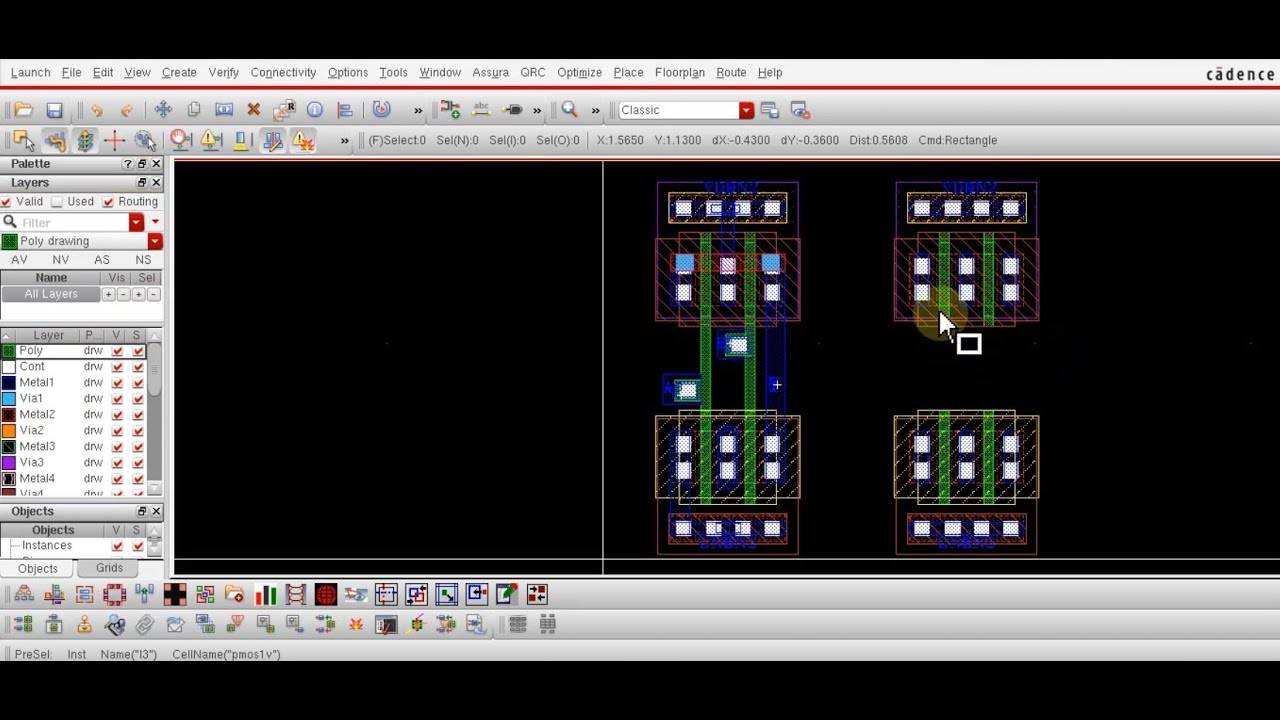

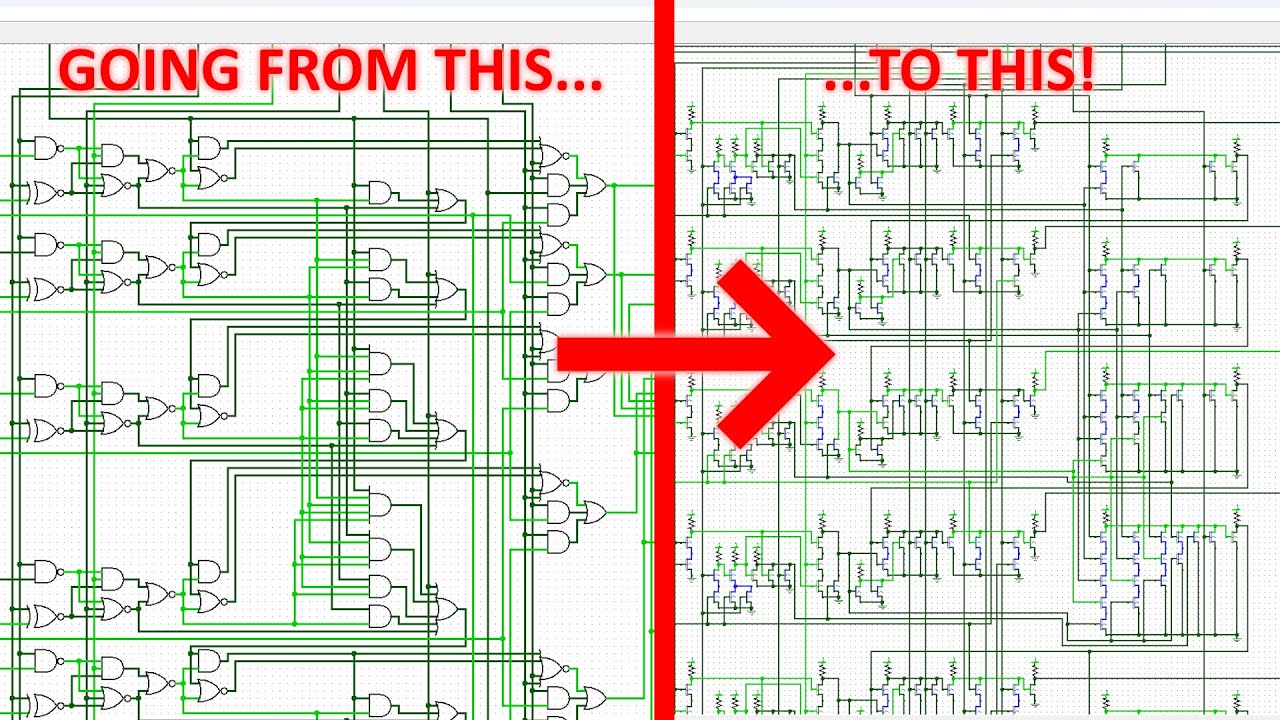

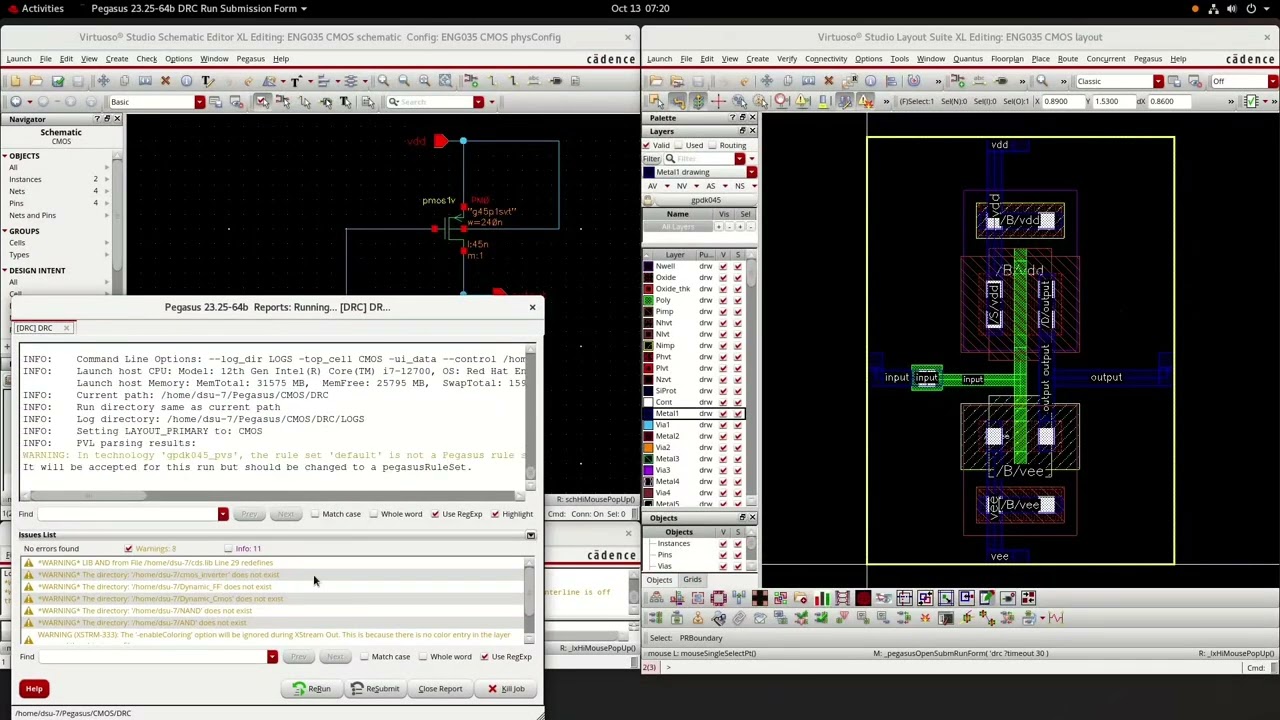

In this tutorial, we move from schematic to layout design in Cadence Virtuoso IC 23, using the gpdk045 technology library. You’ll learn how to draw a CMOS layout, run Design Rule Check (DRC), and perform Layout Versus Schematic (LVS) verification using Pegasus.

This experiment bridges the gap between circuit design and physical implementation—an essential step in modern VLSI design flow.

🔑 What you’ll learn

1. Creating CMOS layout in Virtuoso Layout Editor

2. Setting up gpdk045 technology library

3. Running DRC in Pegasus and resolving layout violations

4. Performing LVS to verify schematic–layout consistency

5. Understanding layout layers and design rules

6. Tips for clean DRC & LVS passes in CMOS layouts

📂 Playlist: Cadence Virtuoso Lab Experiments

👉 Part of our “Learn Cadence from Basics” series covering transistor-to-layout CMOS VLSI design.

🔔 Subscribe for more tutorials on layout design, VLSI flow, and Cadence tools.

Note: This tutorial is recorded using the Cadence Virtuoso IC 23 software, licensed under Dayananda Sagar University.

CMOS Inverter transient and dc analysis • Transient and dc analysis of CMOS invertor...

#CadenceVirtuoso

#CMOSLayout

#PegasusDRC

#LVSVerification

#gpdk045

#VLSI

#LearnCadenceFromBasics

#TronicWorksTech

Повторяем попытку...

Доступные форматы для скачивания:

Скачать видео

-

Информация по загрузке: