FSM Sequence Detector for 00111 (Part 2: D Flip-Flop Circuit Design)

Автор: The Computer Engineering Notebook

Загружено: 2025-12-13

Просмотров: 25

Описание:

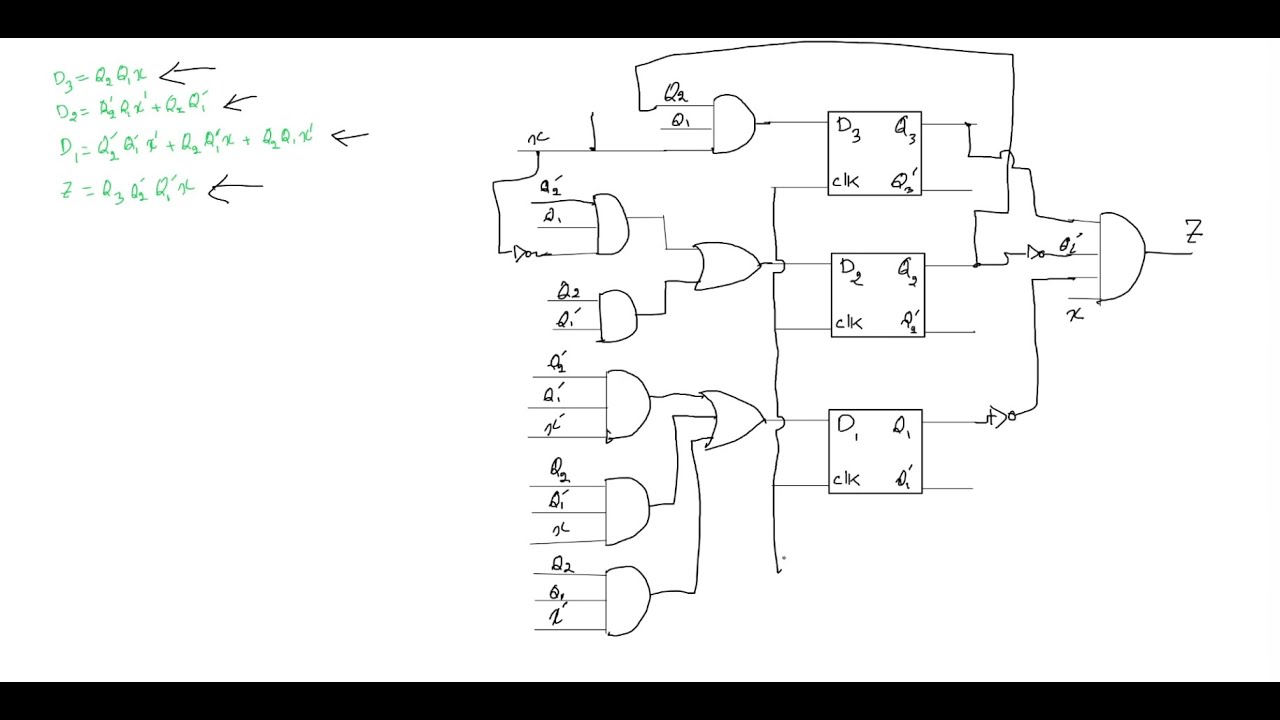

In this digital logic design tutorial, I complete the design of a synchronous sequential circuit (Finite State Machine) that detects the input sequence 00111.

What we cover in Part 2:

Using the state transition table from Part 1 to derive the next-state equations

Designing the complete FSM using D flip-flops

Implementing the combinational logic with AND, OR, and NOT gates

Using don’t-care conditions for unused states to simplify Karnaugh maps

Connecting everything together to form the final sequence detector circuit

This video shows how to go from FSM theory to a complete hardware-level implementation.

Note: Unused states are treated as don’t-care conditions in the Karnaugh maps to allow optimal logic simplification.

🔗 Watch Part 1 (State Diagram & Transition Table):

👉 • FSM Sequence Detector for 00111 (Part 1: S...

🎥 Related Tutorial (Sequence 0011):

👉 • FSM Finite State Machine: Sequence 0010 Us...

Повторяем попытку...

Доступные форматы для скачивания:

Скачать видео

-

Информация по загрузке:

![Почему работает теория шести рукопожатий? [Veritasium]](https://image.4k-video.ru/id-video/ggI1xKzoANs)