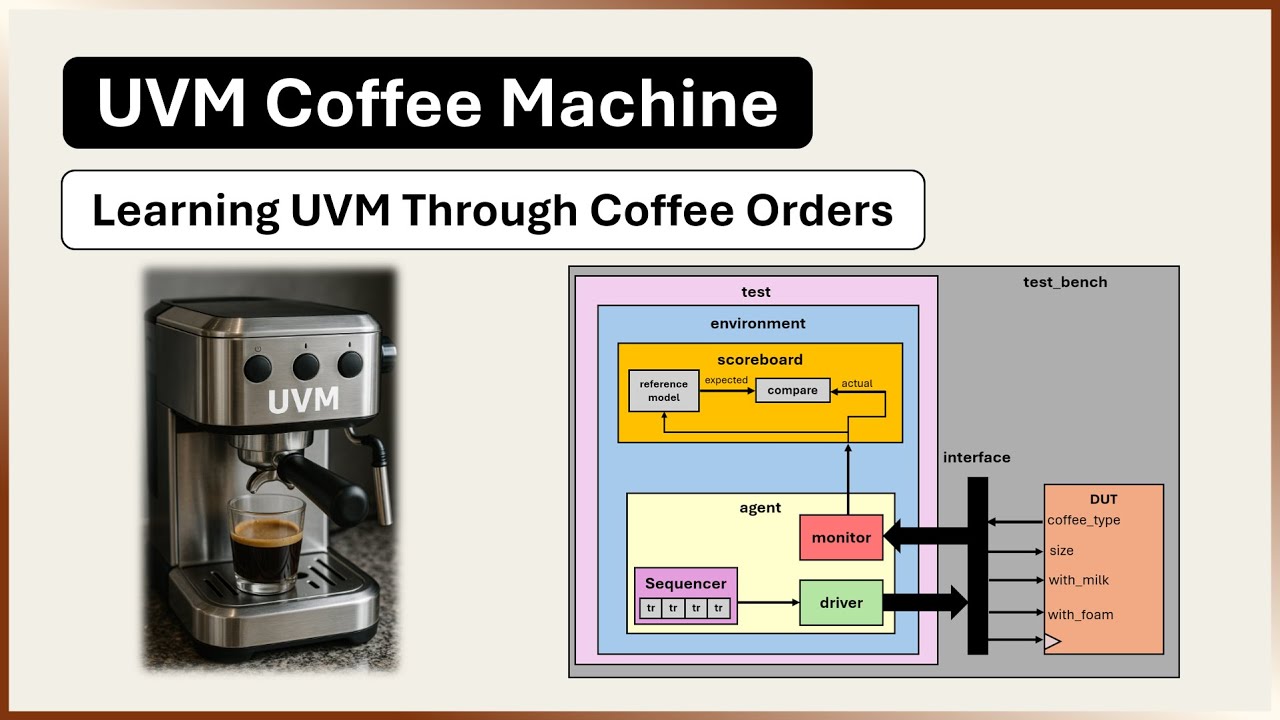

Введение в UVM — универсальная методология верификации для SystemVerilog.

Автор: Doulos Training

Загружено: 2011-03-29

Просмотров: 122951

Описание:

Джон Эйнсли, соучредитель и технический специалист компании Doulos, дает краткий обзор UVM — универсальной методологии верификации для функциональной верификации с использованием SystemVerilog.

Это лишь один из серии обучающих видеороликов по UVM, остальные видео из плейлиста смотрите здесь: • Easier UVM Video Tutorial

Компания Doulos проводит запланированные онлайн- и очные занятия, а также организует выездные командные тренинги и интерактивные онлайн-мероприятия по всему миру – самую актуальную информацию вы можете найти на нашем сайте: https://www.doulos.com

ПОПУЛЯРНЫЕ ОБУЧЕНИЯ ПО UVM

Курс для начинающих пользователей UVM: https://bit.ly/3X4LlWi

Комплексный курс по System Verilog: https://bit.ly/3Cp89qx

Чтобы узнать о тренингах для вас или вашей команды: https://bit.ly/3WZ9a1W

Подпишитесь на наш канал @DoulosTraining, чтобы получать больше информации:

Вводные видеоролики по самым популярным темам обучения – System Verilog, UVM, SystemC и TLM-2.0, VHDL, Python и глубокое обучение, а также Arm.

— Ответы на часто задаваемые вопросы и инструкции.

— Наши последние вебинары в прямом эфире и по запросу (и ссылки для подключения).

Подпишитесь (и настройте уведомления): https://bit.ly/3MYWzsk

Подписывайтесь на нас в Twitter: @DoulosTraining

Подписывайтесь на нас в LinkedIn: / doulo. .

Повторяем попытку...

Доступные форматы для скачивания:

Скачать видео

-

Информация по загрузке: