Analysis and Design of Low Power Reversible Carry Select Adder Using D Latch final year projects in

Автор: TRU PROJECTS

Загружено: 2020-09-21

Просмотров: 179

Описание:

TO PURCHASE OUR PROJECTS IN ONLINE

CONTACT : TRU PROJECTS

WEBSITE : www.truprojects.in

MOBILE : 9676190678

MAIL ID : [email protected]

ABSTRACT :

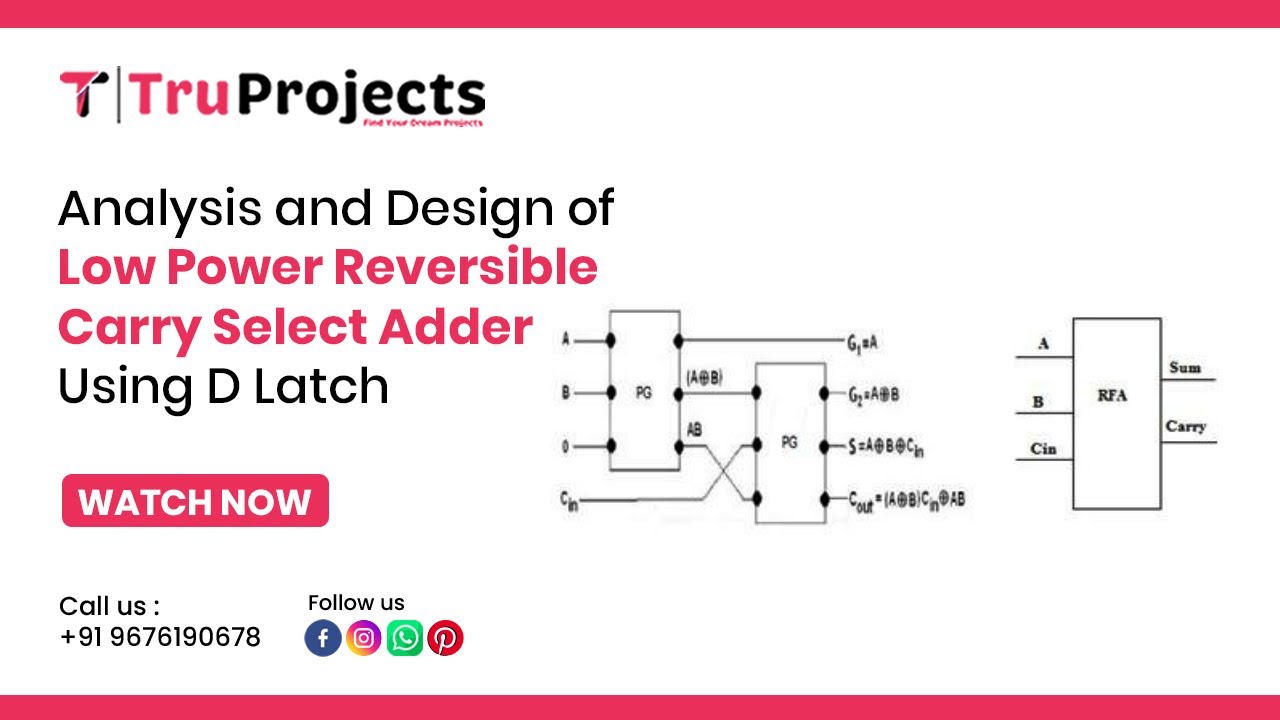

Most important design parameter in integrated circuit

is Power dissipation after speed. Adders are one of the basic

fundamental component in such circuit, designing much efficient

Adder results in optimizing whole circuit. Due to rapid growth in

technology there is a need of fast processing arithmetic unit, so

Carry Select Adder (CSLA) is one of the fast processing adder.

By observing the CSLA circuitry it is noticed that, further

optimization can be achieved in various criteria. Power

dissipation results only when bits are lost while processing, as per

Launder’s principle, KTln2 heat is dissipated if there is any loss

in bit. Since conventional CSLA is designed using irreversible

logic gates which it results much more power dissipation but it

can be overcome by employing reversible logic to reduce power

dissipation till some extent. By using this idea, following paper

proposes a efficient technique to design 8-bit CSLA using

reversible logic, for this purpose this paper undertakes 8-bit

CSLA with D Latch.. This paper evaluates the proposed design

in-terms of power, delay, garbage output, quantum cost and

number of gates using 90nm CMOS process technology for nbits. All the works related to proposed design carried in cadence

virtuoso tool and by comparing the simulation results and

analysis this paper observed that, proposed reversible CSLA

using D-latch attains low power dissipation which is equal to

94.68uW,which shows decrease in 59.175%than irreversible

CSLA using D-latch.

Повторяем попытку...

Доступные форматы для скачивания:

Скачать видео

-

Информация по загрузке:

![Почему работает теория шести рукопожатий? [Veritasium]](https://image.4k-video.ru/id-video/ggI1xKzoANs)

![Детектирование виртуальных машин: как оно работает и как его обходят [RU]](https://image.4k-video.ru/id-video/W-KGmGH_IZ4)