Design and Performance Analysis of 8-Bit Carry Select Adder Using Hybrid Full Adder | VLSI Project

Автор: LifeUnFiltered

Загружено: 2025-10-24

Просмотров: 62

Описание:

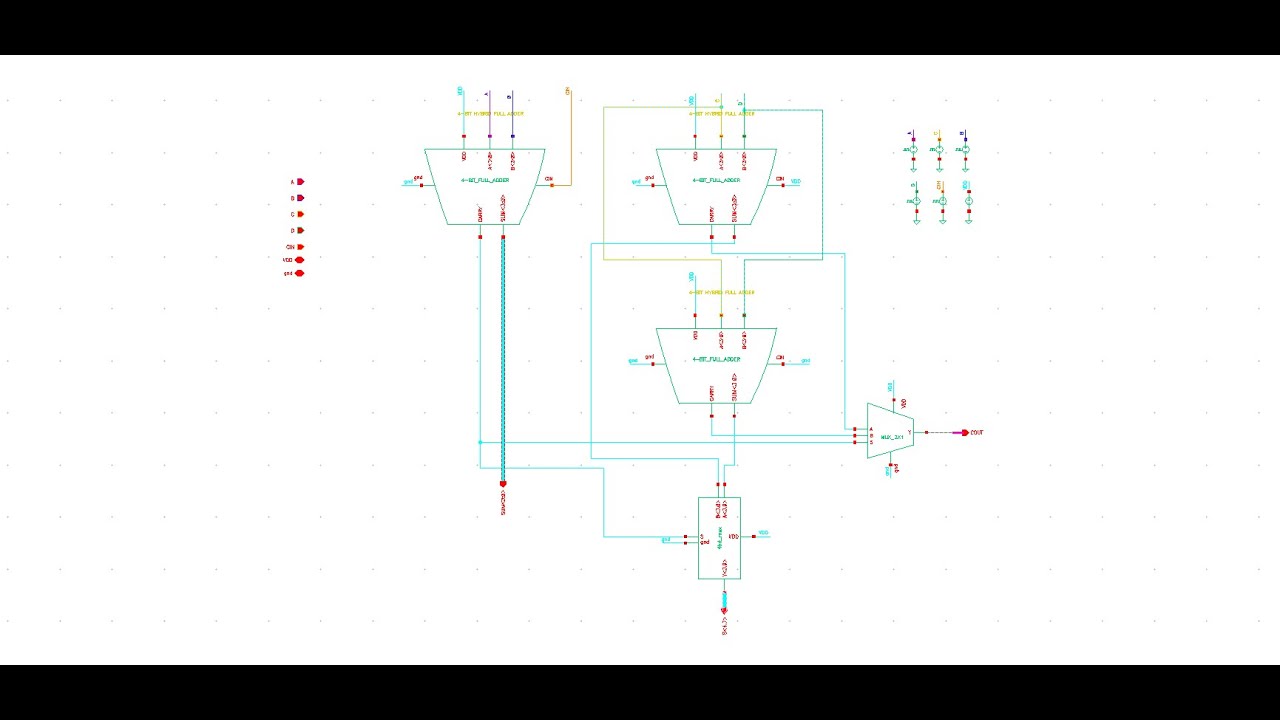

This video presents our IEEE research paper titled “Design and Performance Analysis of 8-Bit Carry Select Adder Using Hybrid Full Adder”, developed as part of our VLSI Design course project at Vidyalankar Institute of Technology. The project focuses on improving the performance of traditional carry select adders by incorporating a Hybrid Full Adder (HFA) structure that combines Gate Diffusion Input (GDI) and Pass Transistor Logic (PTL) techniques. The entire design was implemented and simulated using Cadence Virtuoso with gpdk180 and gpdk90 process technologies.

Through detailed schematic design and transient simulations, we evaluated key performance parameters such as propagation delay, power consumption, power-delay product (PDP), and area efficiency. The proposed 8-bit CSLA demonstrates notable improvements in speed and power optimization compared to conventional CSLA and Ripple Carry Adder (RCA) architectures, making it highly suitable for low-power and high-speed VLSI applications such as DSP processors and arithmetic logic units.

This work was carried out by Samiksha Chavan and Himanshu Shinde, under the guidance of Prof. Akhil Masurkar, from the Department of Electronics and Computer Science Engineering, Vidyalankar Institute of Technology.

Повторяем попытку...

Доступные форматы для скачивания:

Скачать видео

-

Информация по загрузке:

![Пожалуй, главное заблуждение об электричестве [Veritasium]](https://image.4k-video.ru/id-video/6Hv2GLtnf2c)